Ang mga counter ay sunud-sunod na mga circuit na ang function ay bilangin ang pulso, dalas at oras ng signal gamit ang isang solong signal ng orasan. Ito ay isang mahalagang bahagi ng digital electronics dahil ang buong elektronikong aparato ay gumagana sa mga counter. Ang mga ito ay dinisenyo sa pamamagitan ng pagpapangkat ng isang (katulad o magkakaibang) hanay ng mga flipflop. Ang mga counter ay nagpapatakbo sa iba't ibang mga mode ng modules, na kinakatawan ng bilang ng mga estado ng cycle. Mayroong dalawang uri ng mga counter , ang mga ito ay magkasabay at asynchronous counter. Nagpapatakbo ang kasabay na counter batay sa signal ng pag-input ng orasan at ang asynchronous counter ay malaya sa signal ng input na orasan. Ang kasabay na counter ay a magparehistro counter na kung saan ay karagdagang naiuri bilang isang ring-type at twisted type ring counter.

Ano ang Ring Counter?

Kahulugan: Ang isang ring counter ay kilala rin bilang SISO ( serial sa serial out ) shift register counter, kung saan ang output ng flip flop ay konektado sa input ng flip flop na kumikilos bilang isang ring counter. Ang pagdidisenyo ng ring counter ay maaaring gawin sa pamamagitan ng paggamit ng apat D-Flip Flops na may isang pangkaraniwang signal ng orasan at ang overriding input ay maaaring konektado sa paunang itinakda at malinaw.

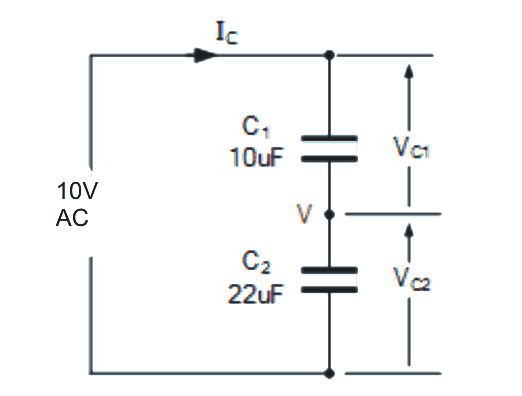

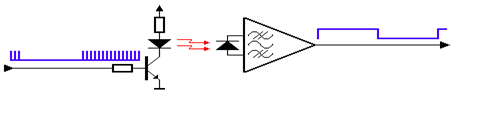

block-diagram-ng-ring-counter

Mula sa diagram sa itaas,

1). Ang bilang ng mga estado na ginamit ay 4 (Kung saan wala sa mga estado = wala ng mga flip flop na ginamit).

2). Paunang itinakda o Malinaw: Ang pangunahing pag-andar nito ay kung nagbago ang signal ng input ng orasan pagkatapos ay nabago din ang halaga ng output.

Ang mga koneksyon ay ginawa tulad ng sumusunod

- Ang isang input ay konektado sa unang flip-flop ff0-Q0,

- Ang isa pang input ay konektado sa CLR ng iba pang tatlong mga flip flop tulad ng ff1, ff2, ff3.

Teoryang Nagtatrabaho

Halimbawa, kumuha tayo ng isang kundisyon kung saan paunang itinakda = '0000' pagkatapos ang mga output na nakuha sa bawat flip flop ay ang mga sumusunod. Para sa FF0, ang output sa Q0 ay '1', samantalang sa iba pang mga flipflop tulad ng ff, ff2, ff3 (na konektado upang i-clear kung saan CLR = 0) ang mga output na nakuha sa Q1 = Q2 = Q3 = '0 ′. Maaari itong maunawaan sa pamamagitan ng pagsunod sa talahanayan ng katotohanan at mga output waveform na nakuha nito kapag naisakatuparan gamit ang Verilog HDL code sa Xilinx software.

Talahanayan ng Katotohanan

O kaya | CLK | Q0 | Q1 | Q2 | Q3 |

Mababang Pulso | X | 1 | 0 | 0 | 0 |

1 | 0 | 0 | 1 | 0 | 0 |

1 | 0 | 0 | 0 | 1 | 0 |

1 | 0 | 0 | 0 | 0 | 1 |

1 | 0 | 1 | 0 | 0 | 0 |

Kung saan

Mga input = ORI at CLK

X = Ang relo ay maaaring maging isang positibong gilid o isang negatibong gilid

Mga output = Q0, Q1, Q2, Q3.

Mula sa talahanayan, maaari nating obserbahan na ang '1' ay inilipat sa pahilis mula Q0 hanggang Q3 at muli ay lilipat pabalik sa 'Q0'. Kaya ipinapakita nito na gumagana ito tulad ng isang ring counter.

Verilog HDL Program para sa Ring Counter

module dff (q, d, c)

output q

input d, c

reg q

pauna

q = 1’b1

laging @ (posedge c)

q = d

end module

module dff1 (q, d, clk)

output q

input d, clk

reg q

pauna

q = 1’b0

laging @ (posedge clk)

q = d

endmodule

module ring (q, clk)

inout [3: 0] q

input clk

dff u1 (q [0], q [3], clk)

dff1 u2 (q [1], q [0], clk)

dff1 u3 (q [2], q [1], clk)

dff1 u4 (q [3], q [2], clk)

end module

Timing Diagram ng Ring Counter

Ang diagram ng tiyempo ng ring counter ay ipinapakita sa ibaba.

tiyempo-diagram-ng-ring-counter

Pag-uuri ng Mga Ring Counter

Ang mga counter counter ay inuri sa dalawa,

Straight Type

Ang alternatibong pangalan ng isang tuwid na uri ay 'isang mainit na counter', kung saan ang output ng pagtatapos ng flip flop ay ibinibigay bilang isang puna sa input ng pagsisimula ng flip flop. Kung saan ang binary digit 0/1 ay ikinalat sa ring form. Dalawang control signal Paunang itinakda (PR) at ang signal ng orasan (CLK) ay ginagamit. Kung saan ang PR ay konektado sa FF 0 at ang CLR ay ibinibigay sa FF3. Ang sumusunod ay ang block diagram ng 4 na yugto ng tuwid na ring counter.

straight-ring-counter

Talaan ng Katotohanan ng Straight Ring Type Counter

true-table-of-straight-type

Timing Diagram ng Straight Type

tiyempo-diagram-ng-tuwid na uri

Baluktot na Uri

Ang kahaliling pangalan ng baluktot na uri ay ang switch ng buntot / paglalakad / counter ng uri ng Johnson. Ang kinumpletong output ng pagtatapos ng flip flop ay puna sa input ng pagsisimula ng flip flop. Kung saan ang daloy ng 1 at 0 na daloy sa ring form. Ang twisted type counter ay gumagamit ng dalawang control signal tulad ng CLK at ORI. Kung saan ang CLK at ORI ay karaniwan sa lahat ng apat na flip flop. Ang sumusunod ay ang block diagram ng 4 na yugto ng baluktot na ring-type counter.

Talaan ng Katotohanan ng Baluktot na Uri

O kaya | CLK | Q0 | Q1 | Q2 | Q3 |

Mababang Pulso | X | 0 | 0 | 0 | 0 |

1 | 1 | 1 | 0 | 0 | 0 |

1 | 1 | 1 | 1 | 0 | 0 |

1 | 1 | 1 | 1 | 1 | 0 |

1 | 1 | 1 | 1 | 1 | 1 |

1 | 1 | 0 | 1 | 1 | 1 |

1 | 1 | 0 | 0 | 1 | 1 |

1 | 1 | 0 | 0 | 0 | 1 |

Timing Diagram ng Baluktot na Uri

Ang diagram ng tiyempo ng baluktot na uri ay ipinapakita sa ibaba.

tiyempo-diagram-ng-johnson-type

Pagkakaiba sa pagitan ng Ring Type Counter at Johnson Type Counter

Ang mga sumusunod ay ang paghahambing sa pagitan ng ring counter at Johnson counter

Ring Counter | Johnson Counter |

| Ang output ng huling flipflop ay ibinibigay bilang input sa pagsisimula ng flip flop. | Ang output ng huling flip-flop ay kinumpleto at ibinigay bilang input sa pagsisimula ng flip flop. |

| Bilang ng mga estado = Bilang ng mga flip flop na ginamit | Kung ang bilang 'n' ng mga flip flop ay ginamit pagkatapos ang '2n' na bilang ng mga estado ay kinakailangan. |

| Input dalas = n | Dalas ng input = f |

| Dalas ng output = f / n | Dalas ng output = f / 2n |

| Kabuuang mga hindi nagamit na estado = (2n- n) | Kabuuang mga hindi nagamit na estado = (2n- 2n) |

Mga kalamangan

Ang mga kalamangan ay

- Maaari itong i-encode at i-decode ang mga lohika

- Ang pagpapatupad ay maaaring gawin gamit ang JK at D flip flop

Mga Dehado

Ang mga dehado ay

- Sa 15 na estado, 4 na estado ang ginagamit

- Hindi nagsisimula sa sarili.

Mga Aplikasyon

Ang mga sumusunod ay ang mga application

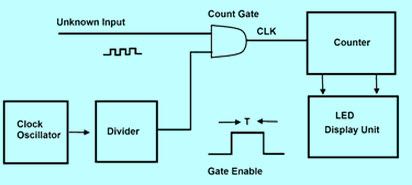

- Counter ng dalas

- ADC

- Mga digital na orasan

- Sukatin ang mga timer at rate, atbp.

FAQ's

1). Ilan ang mga estado doon sa 10-bit ring counter?

10 estado ang ginagamit sa 10-bit ring counter.

2). Ano ang asynchronous counter?

Ang isang asynchronous counter ay nagpapatakbo ng asynchronous na ito ay malaya sa orasan ng pulso. Mayroon itong 2n - 1 estado.

3). Ano ang isang mod ng isang counter?

Ang isa pang pangalan para sa isang mod counter ay ang Modulus counter. Ito ay tinukoy bilang ang bilang ng mga estado sa isang counter.

4). Ano ang ibig mong sabihin sa counter ni Johnson?

Ang Johnson counter ay isang uri ng ring counter, kung saan ang output ng huling flip-flop ay kinumpleto at puna sa pag-input ng unang flip-flop. Ang bilang ng mga estado na ginamit ay 2n.

5). Ano ang paghati sa pamamagitan ng N counter?

Hinahati sa pamamagitan ng N counter ay nangangahulugang ang paghahati ng dalas ng input ng orasan ng N.

6). Ano ang ibig mong sabihin sa pamamagitan ng SISO shift register?

Ang isang rehistro ng SISOshift ay isang serial na in-serial out ang rehistro, kung saan ang data ng pag-input at data ng output ay naproseso nang serial isa pagkatapos ng isa pa at ang resulta ay nakaimbak sa rehistro.

Kaya, isang counter ay isang mahalagang bahagi ng mga digital electron. Ang mga ito ay inuri bilang magkasabay (singsing-uri at baluktot na uri) at asynchronous counter. Kaya, ito ay isang pangkalahatang ideya ng isang ring counter na gumagamit ng dalawang control signal, orasan at paunang-set. Batay sa mga signal na ito ay nagpapatakbo sila sa ring format kaya't ito ay tinatawag na ring counter, higit na nauuri ito bilang isang tuwid at baluktot na uri. Kung saan ang bawat counter ay may sariling disenyo, pakinabang, at kawalan.