Ang isang unijunction transistor ay isang 3 terminal semiconductor aparato na hindi katulad ng isang BJT ay mayroon lamang isang solong pn junction. Karaniwang dinisenyo ito upang magamit bilang isang solong-yugto oscillator circuit para sa pagbuo ng mga pulsed signal na angkop para sa mga digital-circuit application.

UJT Relaxation Oscillator Circuit

Ang unijunction transistor ay maaaring karaniwang naka-wire sa anyo ng isang oscillator ng pagpapahinga tulad ng ipinakita sa sumusunod na pangunahing circuit.

Dito gumagana ang mga sangkap na RT at CT tulad ng mga elemento ng tiyempo at tinutukoy ang dalas o ang rate ng osilasyon ng UJT circuit.

Para sa pagkalkula ng dalas ng oscillating maaari naming gamitin ang sumusunod na formula, na isinasama ang unijunction transistor intrinsic stand-off ratio ang bilang isa sa mga parameter kasama ang RT at CT para sa pagtukoy ng mga oscillating pulses.

Ang karaniwang halaga ng stand-off ratio para sa isang tipikal na aparato ng UJT ay nasa pagitan ng 0.4 at 0.6 . Kaya't isinasaalang-alang ang halaga ng ang = 0.5, at pinapalitan ito sa equation sa itaas na nakukuha namin:

Kapag ang supply ay nakabukas SA, ang boltahe sa pamamagitan ng risistor RT ay naniningil ng capacitor CT patungo sa antas ng supply na VBB. Ngayon, ang stand-off voltage Vp ay natutukoy ng Vp sa kabuuan ng B1 - B2, kasabay ng pagsubok ng stand-off na UJT ang bilang: Vp = ang VB1VB2 - VD.

Sa sobrang haba ng boltahe VE sa kabuuan ng capacitor ay mananatiling mas mababa kaysa sa Vp, ang mga terminal ng UJT sa kabuuan ng B1, B2 ay nagpapakita ng isang bukas na circuit.

Ngunit sa sandaling ang boltahe sa CT ay lampas sa Vp, ang unijunction transistor ay nagpaputok, na mabilis na naglalabas ng capacitor, at nagpapasimula ng isang sariwang ikot.

Sa panahon ng pagpapaputok na halimbawa ng UJT, nagreresulta sa potensyal sa kabuuan ng R1 na tumaas, at ang potensyal sa kabuuan ng R2 na babagsak.

Ang nagreresultang waveform sa kabuuan ng emitter ng UJT ay gumagawa ng isang signal ng sawtooth, na nagpapakita ng isang potensyal na positibong pagpunta sa B2, at isang potensyal na negatibong pagpunta sa B1 na humantong sa UJT

Mga Lugar ng Application ng Unijunction Transistor

Ang mga sumusunod ay ang pangunahing mga lugar ng aplikasyon kung saan malawak na ginagamit ang mga unijunction transistor.

- Pag-trigger ng Circuits

- Mga Oscillator Circuits

- Boltahe / Kasalukuyang Regulated supplies.

- Mga Circuits na batay sa timer,

- Mga Sawtooth Generator,

- Mga Circuit Control ng Phase

- Bistable network

Pangunahing Mga Tampok

Madaling Ma-access at Mura : Ang murang presyo at madaling pagkakaroon ng mga UJT kasama ang ilang mga pambihirang tampok ay humantong sa isang malawak na pagpapatupad ng aparatong ito sa maraming mga elektronikong aplikasyon.

Mababang Pagkonsumo ng Lakas : Dahil sa kanilang isang tampok na mababang paggamit ng kuryente sa ilalim ng normal na mga kondisyon sa pagtatrabaho, ang aparato ay isinasaalang-alang bilang isang hindi kapani-paniwalang tagumpay sa patuloy na pagsisikap na bumuo ng makatwirang mahusay na mga aparato.

Lubhang matatag na Maaasahang Operasyon : Kapag ginamit bilang isang oscillator o sa pagkaantala ng pag-trigger ng circuit, gumagana ang UJT na may matinding pagiging maaasahan at may isang tumpak na tugon sa output.

Unijunction Transistor Pangunahing Konstruksiyon

Larawan # 1

Ang UJT ay isang aparato na tatlong-terminal na semiconductor na nagsasama ng isang simpleng konstruksyon na nakalarawan sa nasa itaas na pigura.

Sa konstruksyon na ito, isang bloke ng banayad na nopop na n-uri ng materyal na silikon (pagkakaroon ng nadagdagang katangian ng paglaban) ay nagbibigay ng isang pares ng mga contact sa base na konektado sa dalawang dulo ng isang ibabaw, at isang pamalo ng aluminyo na nakaayos sa tapat na likuran.

Ang p-n junction ng aparato ay nilikha sa hangganan ng aluminyo baras at ang n-uri ng silicon block.

Ang nabuo na solong p-n junction na ito ay ang dahilan para sa pangalan ng aparato na 'unijunction' . Ang aparato ay unang kilala bilang duo (dobleng) base diode dahil sa paglitaw ng isang pares ng mga base contact.

Pansinin na sa itaas na pigura na ang baras ng aluminyo ay fuse / pagsasama sa bloke ng silikon sa isang posisyon na mas malapit sa contact ng base 2 kaysa sa contact na 1, at pati na rin ang base 2 na terminal ay naging positibo patungkol sa base 1 terminal sa pamamagitan ng VBB volts. Kung paano maiimpluwensyahan ng mga aspektong ito ang pagtatrabaho ng UJT ay magiging maliwanag sa mga sumusunod na seksyon

Simbolikong Kinatawan

Ang makasagisag na representasyon ng unijunction transistor ay makikita sa larawan sa ibaba.

Figure 2

Pagmasdan na ang emitter terminal ay ipinapakita na may isang anggulo sa tuwid na linya na naglalarawan ng bloke ng n-type na materyal. Makikita ang ulo ng arrow na nakadidirekta sa direksyon ng karaniwang kasalukuyang (butas) na daloy habang ang unijunction aparato ay nasa pasulong, na-trigger, o nagsasagawa ng kundisyon.

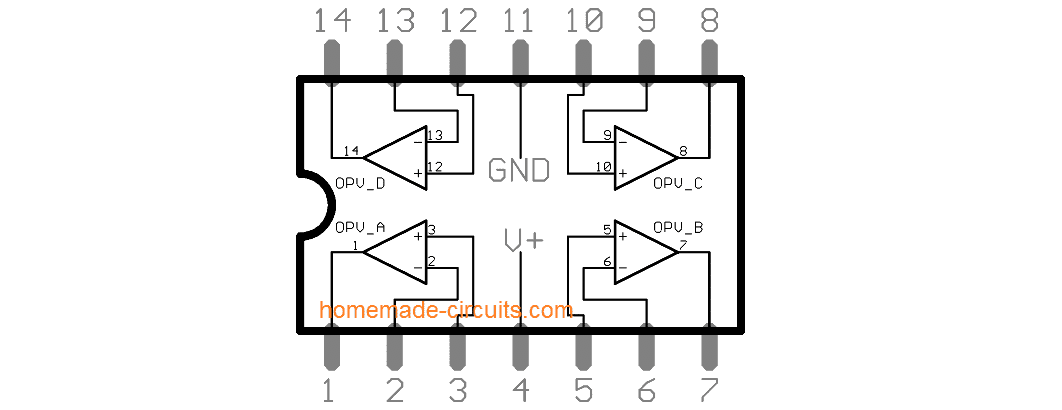

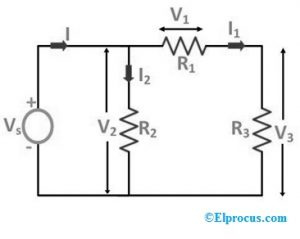

Unijunction Transistor Equivalent Circuit

Larawan # 3

Ang katumbas na UJT circuit ay maaaring masaksihan sa ipinakita sa itaas na imahe. Maaari naming makita kung gaano ka simple ang katumbas na circuit na ito, na nagsasama ng isang pares ng resistors (isang naayos, isang naaayos) at isang nag-iisa na diode.

Ang resistensya RB1 ay ipinapakita bilang isang madaling iakma risistor isinasaalang-alang ang halaga nito ay magbabago ng kasalukuyang pagbabago ng IE. Sa totoo lang, sa anumang transistor na kumakatawan sa isang unijunction, ang RB1 ay maaaring magbagu-bago mula 5 kΩ hanggang 50 Ω para sa anumang katumbas na pagbabago ng IE mula 0 hanggang 50 = μA. Ang interbase resistance RBB ay kumakatawan sa paglaban ng aparato sa pagitan ng mga terminal B1 at B2 kapag IE = 0. Sa pormula para dito,

RBB = (RB1 + RB2) | IE = 0

Ang saklaw ng RBB ay karaniwang nasa loob ng 4 at 10 k. Ang paglalagay ng aluminyo baras tulad ng ipinakita sa unang pigura ay nagbibigay ng kamag-anak na magnitude ng RB1, RB2 kapag IE = 0. Maaari nating tantyahin ang halaga ng VRB1 (kapag IE = 0) gamit ang batas ng boltahe-divider, tulad ng ibinigay sa ibaba:

VRB1 = (RB1 x VBB) / (RB1 + RB2) = ηVBB (na may IE = 0)

Ang liham na Greek ang Ang (eta) ay kilala bilang intrinsic stand-off ratio ng unijunction transistor device at tinukoy ng:

η = RB1 / (RB1 + RB2) (na may IE = 0) = RB1 / RBB

Para sa ipinahiwatig na boltahe ng emitter (VE) na mas mataas kaysa sa VRB1 (= ηVBB) ng pasulong na pagbagsak ng boltahe ng diode na VD (0.35 → 0.70 V), ang diode ay mag-uudyok SA. Mainam na maaari nating ipalagay ang kundisyon ng maikling circuit, tulad na magsisimulang magsagawa ang IE sa pamamagitan ng RB1. Sa pamamagitan ng equation, ang nagpapalitaw na antas ng boltahe ng emitter ay maaaring ipahayag bilang:

VP = ηVBB + VD

Pangunahing Katangian at Paggawa

Ang mga katangian ng isang kinatawan na unijunction transistor para sa VBB = 10 V ay ipinahiwatig sa pigura sa ibaba.

Larawan # 4

Maaari nating makita iyon, para sa potensyal na emitter na nakasaad sa kaliwang bahagi ng tuktok na punto, ang halaga ng IE ay hindi hihigit sa IEO (na nasa microamperes). Ang kasalukuyang IEO higit pa o mas mababa ay sumusunod sa reverse leakage kasalukuyang ICO ng maginoo bipolar transistor.

Ang rehiyon na ito, ay tinukoy bilang rehiyon ng cutoff, tulad ng ipinahiwatig din sa igos.

Sa lalong madaling nakamit ang pagpapadaloy sa VE = VP, ang potensyal na emitter na VE ay bumababa habang tumataas ang potensyal ng IE, na tiyak na alinsunod sa pagbawas ng paglaban ng RB1 para sa pagtaas ng kasalukuyang IE, tulad ng ipinaliwanag dati.

Ang katangiang nasa itaas ay nagbibigay ng isang unijunction transistor na may isang lubos na matatag na rehiyon ng negatibong paglaban, na nagbibigay-daan sa aparato na gumana at mailapat nang may matinding pagiging maaasahan.

Sa panahon ng proseso sa itaas, ang point ng lambak ay maaaring asahan na sa wakas ay makakamit, at ang anumang pagtaas sa IE na lampas sa saklaw na ito ay sanhi ng pagpasok ng aparato sa rehiyon ng saturation.

Ang figure # 3 ay nagpapakita ng isang diode na katumbas na circuit sa parehong rehiyon na may isang katulad na diskarte sa mga katangian.

Ang pagbagsak sa halaga ng paglaban ng aparato sa aktibong rehiyon ay sanhi sa account ng mga na-injected na butas sa n-type block ng p-type na aluminyo rod sa oras na maganap ang pagpapaputok ng aparato. Nagreresulta ito sa isang pagtaas sa dami ng mga butas sa seksyong n-type na nagdaragdag ng libreng numero ng mga electron, na nagdudulot ng isang pinahusay na conductivity (G) sa buong aparato na may katumbas na pagbaba ng paglaban nito (R ↓ = 1 / G ↑)

Mahalagang Parameter

Mahahanap mo ang tatlong karagdagang mahahalagang parameter na nauugnay sa isang unijunction transistor na kung saan ay IP, VV, at IV. Ang lahat ng ito ay ipinahiwatig sa figure # 4.

Ang mga ito ay talagang madaling maunawaan. Ang normal na umiiral na katangian ng emitter ay maaaring matutunan mula sa ibaba ng numero # 5.

Larawan # 5

Mapapansin natin dito na ang IEO (μA) ay hindi napapansin dahil ang pahalang na sukat ay na-calibrate sa milliamperes. Ang bawat kurba na tumatawid sa patayong axis ay ang kaukulang mga resulta ng VP. Para sa pare-pareho na mga halaga ng η at VD, ang halaga ng VP ay nagbabago alinsunod sa VBB, tulad ng formulated sa ibaba:

Unijunction Transistor Datasheet

Ang isang karaniwang saklaw ng mga panteknikal na panoorin para sa UJT ay maaaring natutunan mula sa Larawan # 5 sa ibaba.

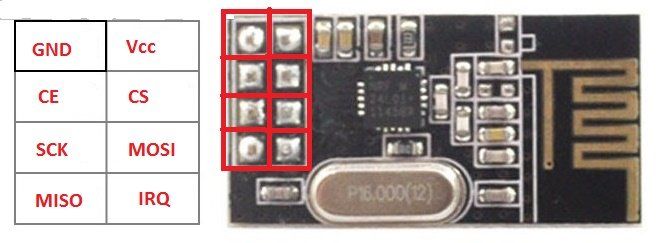

Mga Detalye ng PINT Pinout

Ang mga detalye ng pinout ay kasama rin sa nasa itaas na datasheet. Pansinin na ang mga base terminal B1 at B2 ay nakatayo sa tapat ng bawat isa habang ang emitter pin AY ay nakaposisyon sa gitna, sa pagitan ng dalawang ito.

Bukod dito, ang base pin na kung saan ay dapat na konektado sa mas mataas na mga antas ng supply ay nakatayo malapit sa off shoot sa kwelyo ng package.

Paano gumamit ng isang UJT para sa Pag-trigger ng isang SCR

Ang isang medyo tanyag na aplikasyon ng UJT ay para sa pagpapalitaw ng aparato ng kuryente tulad ng SCR. Ang pangunahing mga sangkap ng ganitong uri ng nagpapalitaw na circuit ay inilalarawan sa ipinakita sa ibaba na diagram # 6.

Larawan # 6: Pag-trigger ng isang SCR gamit ang isang UJT

Larawan # 7: UJT Load na linya para sa isang pag-trigger para sa isang panlabas na aparato tulad ng SCR

Ang pangunahing mga sangkap ng tiyempo ay nabuo ng R1 at C, habang ang R2 ay gumagana tulad ng isang pull down resistors para sa output na nag-trigger ng boltahe.

Paano Makalkula ang R1

Ang risistor R1 ay dapat kalkulahin upang magarantiyahan na ang linya ng pag-load na tinukoy ng R1 ay naglalakbay sa pamamagitan ng mga katangian ng aparato sa loob ng negatibong rehiyon ng paglaban, ibig sabihin, patungo sa kanang bahagi ng tuktok na punto ngunit sa kaliwang bahagi ng lambak na punto tulad ng ipinahiwatig Larawan # 7.

Kung ang linya ng pag-load ay hindi makatawid sa kanang bahagi ng tuktok na punto, ang unijunction na aparato ay hindi maaaring magsimula.

Ang formula na R1 na ginagarantiyahan ang isang kondisyon ng switch ON ay maaaring matukoy sa sandaling isasaalang-alang namin ang tuktok na punto kung saan ang IR1 = IP at VE = VP. Ang equation IR1 = IP ay mukhang lohikal sapagkat ang kasalukuyang singilin ng capacitor, sa puntong ito, ay zero. Ibig sabihin, ang kapasitor sa tukoy na puntong ito ay lumilipat sa pamamagitan ng isang singilin sa isang naglalabas na kondisyon.

Para sa kondisyon sa itaas maaari naming magsulat:

Bilang kahalili, upang magagarantiyahan ang isang kumpletong SCR na patayin:

R1> (V - Vv) / Iv

Ipinapahiwatig nito na ang saklaw ng pagpili ng resistor R1 ay dapat na ipahayag tulad ng ibinigay sa ibaba:

(V - Vv) / Iv

Paano Makalkula ang R2

Ang risistor R2 ay dapat na sapat na maliit upang matiyak na ang SCR ay hindi maling na-trigger ng boltahe VR2 sa kabuuan ng R2 kapag ang IE ≅ 0 Amp. Para sa mga ito ang VR2 ay dapat na kalkulahin ayon sa sumusunod na pormula:

VR2 ≅ R2V / (R2 + RBB) (kapag IE ≅ 0)

Ang capacitor ay nagbibigay ng pagkaantala ng oras sa pagitan ng mga nagti-trigger na pulso, at natutukoy din ang haba ng bawat pulso.

Paano Makalkula C

Sumangguni sa figure sa ibaba, sa lalong madaling ang circuit ay pinalakas, ang boltahe VE na katumbas ng VC ay magsisimulang singilin ang capacitor patungo sa boltahe VV, sa pamamagitan ng isang oras na pare-pareho τ = R1C.

Larawan # 8

Ang pangkalahatang equation na tumutukoy sa tagal ng pagsingil ng C sa isang UJT network ay:

vc = Vv + (V - Vv) (1 - ay-t / R1C)

Sa pamamagitan ng aming nakaraang mga kalkulasyon alam na namin ang volatge sa buong R2 sa panahon ng pagsingil sa itaas ng capacitor. Ngayon, kapag vc = vE = Vp, ang aparato ng UJT ay papasok sa switch ON na estado, na nagiging sanhi ng paglabas ng capacitor sa pamamagitan ng RB1 at R2, na may rate depende sa pare-pareho sa oras:

τ = (RB1 + R2) C

Ang sumusunod na equation ay maaaring magamit para sa pagkalkula ng oras ng paglabas kung kailan

vc = vE

ikaw ≅ Vpe -t / (RB1 + R2) C

Ang equation na ito ay naging medyo kumplikado dahil sa RB1, na dumadaan sa pagbawas ng halaga habang tumataas ang kasalukuyang emitter, kasama ang iba pang mga aspeto sa circuit tulad ng R1 at V, na nakakaapekto rin sa rate ng paglabas ng C sa pangkalahatan.

Sa kabila nito, kung mag-refer kami sa katumbas na circuit tulad ng ibinigay sa itaas ng Larawan # 8 (b), karaniwang ang mga halaga ng R1 at RB2 ay maaaring maging tulad ng isang Thévenin network para sa pagsasaayos sa paligid ng capacitor C ay maaaring apektado ng kaunti sa R1, Resistors ng RB2. Bagaman ang boltahe V ay lilitaw na malaki, ang resistive divider na tumutulong sa Thévenin boltahe ay maaaring pangkalahatang hindi pansinin at maalis, tulad ng ipinakita sa ibabang nabawas na katumbas na diagram:

Samakatuwid, ang pinasimple na bersyon sa itaas ay tumutulong sa amin upang makuha ang sumusunod na equation para sa phase ng paglabas ng capacitor C, kapag ang VR2 ay nasa rurok nito.

VR2 ≅ R2 (Vp - 0.7) / R2 + RB1

Para sa higit pang mga circuit ng application maaari mo rin sumangguni sa artikulong ito

Nakaraan: Mini Transceiver Circuit Susunod: PIR Burglar Alarm Circuit